發(fā)布時間:2025-05-30作者來源:金航標瀏覽:670

USB接口是我們HW設計中使用的比較多的一個電路模塊,特別是在醫(yī)療電子,商業(yè)電子電路中使用的比較多,以下我們來分享下USB接口和相對應的電路設計。

USB接口理論認識:

USB(Universal Serial Bus)通用串行總線,USB接口現(xiàn)在大致可以分為USB2.0,USB3.0,USB4(需要注意的是它的正式書寫名字不包含空格也沒有小數(shù)點,即不是USB 4,也不是USB4.0。USB4規(guī)范使用雙鏈路通道,傳輸帶寬達到40Gbps,接口類型為雙向USB-C)。其中我們現(xiàn)在大部分使用的還是USB2.0和USB 3.2 Gen 1(前稱為USB 3.0,后來重新命名為USB 3.1 Gen 1,最終被稱為USB 3.2 Gen 1。)USB 3.2 Gen 2前稱為USB 3.1,后改名為USB 3.2 Gen 2。與Gen 1相比,Gen 2在速度上有所提升。最大傳輸速度:10 Gbps,是Gen 1速度的兩倍,稱為SuperSpeed+。兼容性:向下兼容USB 3.2 Gen 1和USB 2.0。接下來我們來詳細介紹下USB2.0和USB3.0在硬件電路設計上的區(qū)分和使用。

|

版本 |

最大傳輸速率 |

最大輸出電流 |

前稱 |

針腳數(shù)量 |

|

USB2.0 |

480Mbps |

500ma |

4個(VBUS/GND/D+/D-) |

|

|

USB3.1 GEN1 |

5Gbps |

900ma(標準端口) |

USB 3.1 Gen 1 和 USB 3.0 |

9個 |

|

USB3.1 GEN2 |

10 Gbps |

900ma(標準端口) |

USB 3.1 Gen 2 |

9個 |

USB硬件電路設計:

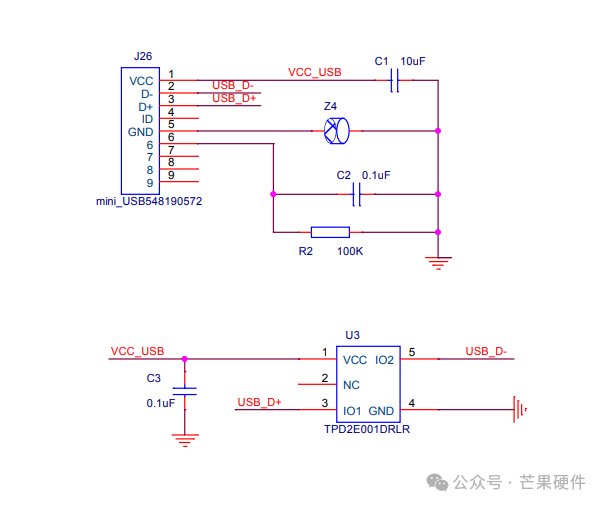

i)USB2.0包含了一組差分信號、一組電源信號(5V電源+GND),4線。

一般而言,上圖的電路設計已經(jīng)可以實現(xiàn)USB數(shù)據(jù)的正常傳輸了。但一般如果考慮EMC方面的話,最好在靠近USB插座端的地方加上共模電感,防止板子內部的高頻干擾通過USB線輻射到外面,對其他的模塊和設備造成電磁干擾。D+、D-以差分方式布線,并通過連續(xù)的參考平面層,保證阻抗的一致性,信號線的差分阻抗Z=90Ω±15%。

另外,稍微提一句USB_OTG(On-The-Go)允許設備在主機和外設角色間切換,通過ID引腳的狀態(tài)確定設備角色。ID pin——當設備檢測到USB_ID信號為低時,該設備應作為Host(主機,也稱A設備)用。當設備檢測到USB_ID信號為高時,該設備作為Slave(外設,也稱B設備)用。

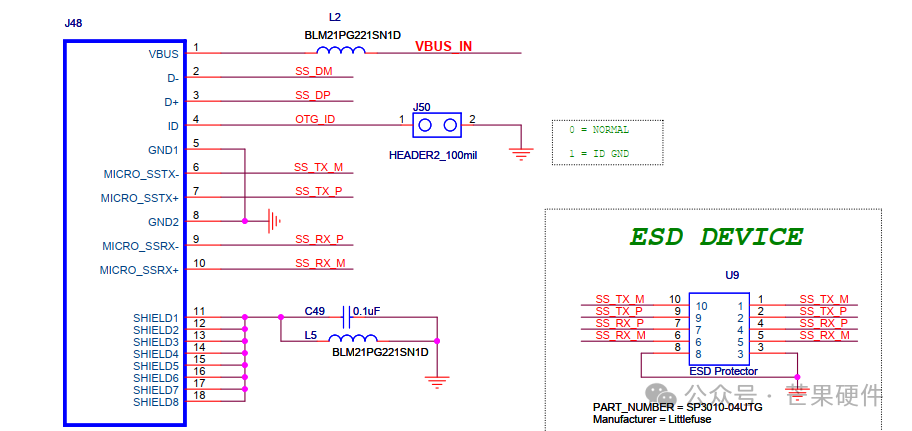

ii)USB3.0包含了一組2.0數(shù)據(jù)差分信號(D-、D+)、一組電源信號(5V電源、GND電源地)、二組3.0數(shù)據(jù)差分信號(RX-、RX+、TX-、TX+)、GND信號地,9線。

USB3.0由于采用的全雙工通信模式(USB2.0 采用半雙工通信模式),數(shù)據(jù)可以同時進行發(fā)送和接收,充分利用了傳輸帶寬,數(shù)據(jù)傳輸速率(5Gbps/10 Gbps)。

DM/DP差分對信號線與USB2.0的連接方式一樣,只要一對一直接連接就可以。信號線的差分阻抗Z=90Ω±10%。另外提醒下USB3.0在選型ESD防護二極管的時候要注意ESD寄生電容要小(0.5pf左右)。

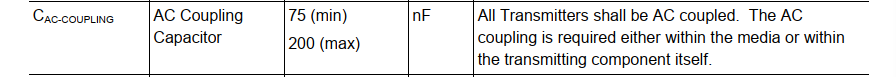

RX-、RX+、TX-、TX+差分對屬于高速serdes差分對,速度5Gbps/10 Gbps。需要在TX端放置100nF隔直電容(協(xié)議中規(guī)定是75nf-200nf),RX端無需放置。host端和device端的偏置直流電壓值不一樣,AC耦合電容起到隔直流作用,也可以更好的預制共模噪聲。

免責聲明:本文采摘自芒果硬件,本文僅代表作者個人觀點,不代表金航標及行業(yè)觀點,只為轉載與分享,支持保護知識產(chǎn)權,轉載請注明原出處及作者,如有侵權請聯(lián)系我們刪除。

品通用logo圖 - 副本.jpg)

品通用logo圖 - 副本.jpg)

品通用logo圖 - 副本.jpg)

品通用logo圖 - 副本.jpg)

品通用logo圖 - 副本.jpg)

Copyright ? 深圳市金航標電子有限公司 版權所有 粵ICP備17113853號